# LIN 2.1 / SAEJ2602-2 Dual LIN Physical Layer

The local interconnect network (LIN) is a serial communication protocol designed to support automotive networks in conjunction with controller area network (CAN). As the lowest level of a hierarchical network, LIN enables cost-effective communication with sensors and actuators when all the features of CAN are not required.

The 33663 product line integrates two physical layer LIN bus dedicated to automotive LIN sub-bus applications. The MC33663LEF and MC33663SEF devices offer normal baud rate (20 kbps) and the MC33663JEF slow baud rate (10 kbps). Both devices integrate fast baud rate (above 100 kbps) for test and programming modes. They present excellent electromagnetic compatibility (EMC) and radiated emission performance, electrostatic discharge (ESD) robustness and safe behavior, in the event of LIN bus short-to-ground or LIN bus leakage during low-power mode.

#### **Features**

- Operational from V<sub>SUP</sub> 7.0 to 18 V DC, functional up to 27 V DC, and handles 40 V during load dump

- · Compatible with LIN protocol specification 2.1, and SAEJ2602-2

- · Very high immunity against electromagnetic interference

- · Low standby current in Sleep mode

- Over-temperature protection

- · Permanent dominant state detection

- Fast baud rate mode selection reported by RXD

- Active bus waveshaping offering excellent radiated emission performance

- Sustains ±15.0 kV ESD IEC6100-4-2 on LIN BUS and VSUP pins

- 5.0 and 3.3 V compatible digital inputs without any external components required

# 33663

#### **DUAL LIN TRANSCEIVER**

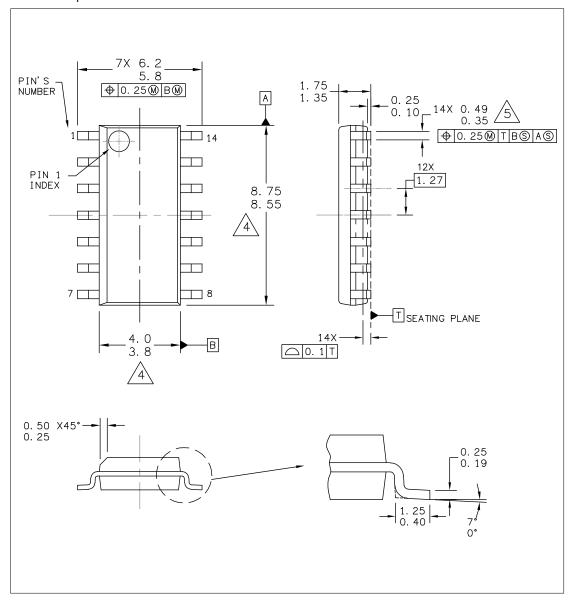

EF SUFFIX (PB-FREE) 98ASB42565B 14-PIN SOICN

| ORDERING INFORMATION                                     |                                        |          |  |  |

|----------------------------------------------------------|----------------------------------------|----------|--|--|

| Device<br>(add an R2 suffix for<br>Tape and reel orders) | Temperature<br>Range (T <sub>A</sub> ) | Package  |  |  |

| MC33663ALEF                                              |                                        |          |  |  |

| MC33663AJEF                                              | -40 to 125°C                           | 14 SOICN |  |  |

| MC33663ASEF                                              |                                        |          |  |  |

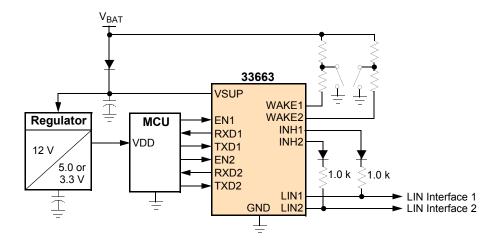

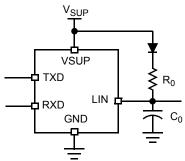

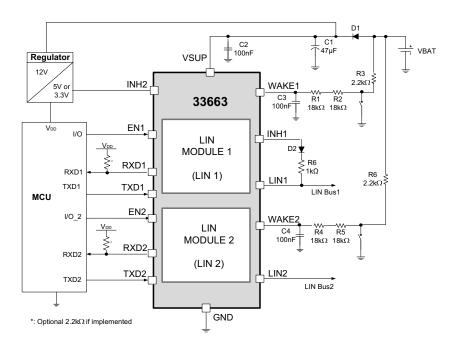

Figure 1. 33663 Simplified Application Diagram

<sup>\*</sup> This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

## **DEVICE VARIATIONS**

**Table 1. Device Variations**

| Freescale Part No.<br>(Add an R2 suffix for<br>Tape and reel orders) | d an R2 suffix for Maximum Baud Rate                                 |               | Package  |

|----------------------------------------------------------------------|----------------------------------------------------------------------|---------------|----------|

| MC33663ALEF                                                          | 20 kbps                                                              |               |          |

| MC33663ASEF                                                          | 20 kbps with restricted limits for transmitter and receiver symmetry | -40 to 125 °C | 14 SOICN |

| MC33663AJEF                                                          | 10 kbps                                                              |               |          |

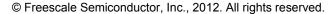

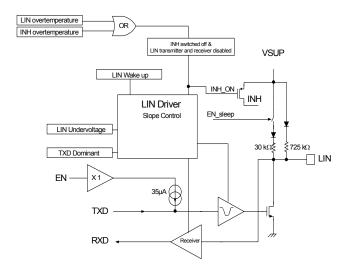

### INTERNAL BLOCK DIAGRAM

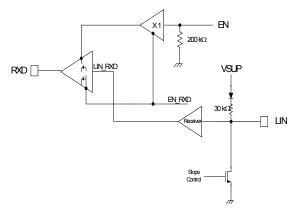

Figure 2. 33663 Simplified Internal Block Diagram

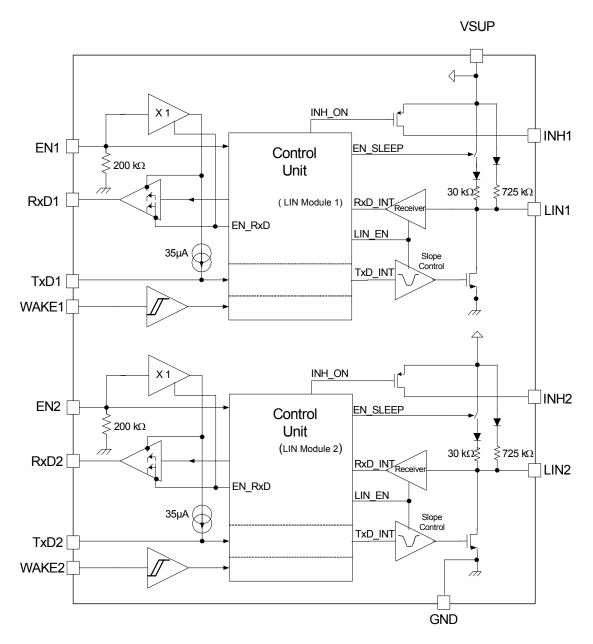

### **PIN CONNECTIONS**

Figure 3. 33663 14-SOIC Pin Connections

Table 2. 33663 Pin Definitions

| Pin | Pin Name | Formal Name    | Definition                                                                                                                                                                                                |

|-----|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | WAKE1    | Wake Input     | This pin is a high-voltage input used to wake-up the LIN1 from Sleep mode.                                                                                                                                |

| 2   | TXD1     | Data Input     | This pin is the transmitter input of the LIN1 interface which controls the state of the bus output.                                                                                                       |

| 3   | LIN1     | LIN Bus        | This bidirectional pin represents the LIN1 single-wire bus transmitter and receiver.                                                                                                                      |

| 4   | LIN2     | LIN Bus        | This bidirectional pin represents the LIN2 single-wire bus transmitter and receiver.                                                                                                                      |

| 5   | INH2     | Inhibit Output | This pin can have two main functions: controlling an external switchable voltage regulator having an inhibit input, or driving an external bus resistor connected to LIN2 in the master node application. |

| 6   | RXD2     | Data Output    | This pin is the receiver output of the LIN2 interface, which reports the state of the bus voltage to the MCU interface.                                                                                   |

| 7   | EN2      | Enable Control | This pin controls the operation mode of the LIN2 interface.                                                                                                                                               |

| 8   | WAKE2    | Wake Input     | This pin is a high-voltage input used to wake-up the LIN2 device from Sleep mode.                                                                                                                         |

| 9   | GND      | Ground         | This pin is the device ground pin.                                                                                                                                                                        |

| 10  | TXD2     | Data Input     | This pin is the transmitter input of the LIN2 interface, which controls the state of the bus output.                                                                                                      |

| 11  | VSUP     | Power Supply   | This pin is device battery level power supply.                                                                                                                                                            |

| 12  | INH1     | Inhibit Output | This pin can have two main functions: controlling an external switchable voltage regulator having an inhibit input, or driving an external bus resistor connected to LIN1 in the master node application. |

| 13  | RXD1     | Data Output    | This pin is the receiver output of the LIN1 interface, which reports the state of the bus voltage to the MCU interface.                                                                                   |

| 14  | EN1      | Enable Control | This pin controls the operation mode of the LIN1 interface.                                                                                                                                               |

#### **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

#### **Table 3. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                                                                                                                                                                                                                                                                                                             | Symbol                                                                                                       | Value                                     | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------|------|

| ELECTRICAL RATINGS                                                                                                                                                                                                                                                                                                                                                  |                                                                                                              |                                           |      |

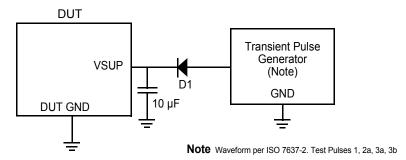

| Power Supply Voltage (VSUP)  Normal Operation (DC)  Transient input voltage with external component (according to ISO7637-2 & ISO7637-3 & "Hardware Requirements for LIN, CAN, and Flexray Interfaces in Automotive Applications" specification Rev. 1.1/December 2nd, 2009) (See Table 4 and Figure 4)                                                             | V <sub>SUP(SS)</sub>                                                                                         | -0.3 to 27                                | V    |

| <ul> <li>Pulse 1 (test up to the limit for Damage - Class A<sup>(1)</sup>)</li> <li>Pulse 2a (test up to the limit for Damage - Class A<sup>(1)</sup>)</li> <li>Pulse 3a (test up to the limit for Damage - Class A<sup>(1)</sup>)</li> <li>Pulse 3b (test up to the limit for Damage - Class A<sup>(1)</sup>)</li> <li>Pulse 5b (Class A)<sup>(1)</sup></li> </ul> | V <sub>SUP(S1)</sub> V <sub>SUP(S2A)</sub> V <sub>SUP(S3A)</sub> V <sub>SUP(S3B)</sub> V <sub>SUP(S5B)</sub> | -100<br>+75<br>-150<br>+100<br>-0.3 to 40 |      |

| Logic Voltage (RXD <sub>1,2</sub> , TXD <sub>1,2</sub> , EN <sub>1,2</sub> Pins)                                                                                                                                                                                                                                                                                    | $V_{LOG}$                                                                                                    | -0.3 to 5.5                               | V    |

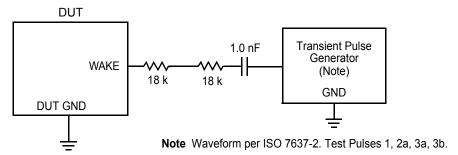

| WAKE (V <sub>WAKE1</sub> ,V <sub>WAKE2</sub> )  Normal Operation with in series 2*18 kΩ resistor (DC)  Transient input voltage with external component (according to ISO7637-2 & ISO7637-3 & "Hardware Requirements for LIN, CAN and Flexray Interfaces in Automotive Applications" specification Rev1.1 / December 2nd, 2009) (See Table 4 and Figure 5)           | V <sub>WAKE(SS)</sub>                                                                                        | -27 to 40                                 | V    |

| <ul> <li>- Pulse 1 (test up to the limit for Damage - Class D<sup>(2)</sup>)</li> <li>- Pulse 2a (test up to the limit for Damage - Class D<sup>(2)</sup>)</li> <li>- Pulse 3a (test up to the limit for Damage - Class D<sup>(2)</sup>)</li> <li>- Pulse 3b (test up to the limit for Damage - Class D<sup>(2)</sup>)</li> </ul>                                   | VWAKE(S1) VWAKE(S2A) VWAKE(S3A) VWAKE(S3B)                                                                   | -100<br>+75<br>-150<br>+100               |      |

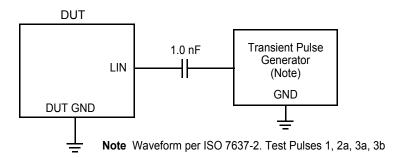

| LIN Bus Voltage (V <sub>LIN1</sub> , V <sub>LIN2</sub> )  Normal Operation (DC)  Transient (Coupled Through 1.0 nF Capacitor) (according to ISO7637-2 & ISO7637-3) (See <u>Table 4</u> and <u>Figure 6</u> )                                                                                                                                                        | V <sub>LIN(SS)</sub>                                                                                         | -27 to 40                                 | V    |

| <ul> <li>- Pulse 1 (test up to the limit for Damage - Class D<sup>(2)</sup>)</li> <li>- Pulse 2a (test up to the limit for Damage - Class D<sup>(2)</sup>)</li> <li>- Pulse 3a (test up to the limit for Damage - Class D<sup>(2)</sup>)</li> <li>- Pulse 3b (test up to the limit for Damage - Class D<sup>(2)</sup>)</li> </ul>                                   | V <sub>LIN(S1)</sub> V <sub>LIN(S2A)</sub> V <sub>LIN(S3A)</sub> V <sub>LIN(S3B)</sub>                       | -100<br>+75<br>-150<br>+100               |      |

- 1. Class A: All functions of a device/system perform as designed during and after exposure to disturbance.

- 2. Class D: At least one function of the Transceiver stops working properly during the test and will return into proper operation automatically when the exposure to the disturbance has ended. No physical damage of the IC occurs.

# ELECTRICAL CHARACTERISTICS MAXIMUM RATINGS

#### **Table 3. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                                                                                                                                                                                        | Symbol                | Value                          | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------|------|

| ELECTRICAL RATINGS                                                                                                                                                                                                                             |                       |                                |      |

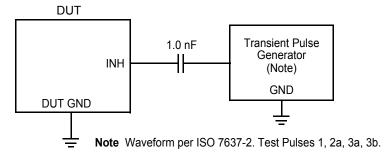

| INH Voltage/Current (V <sub>INH1</sub> , V <sub>INH2</sub> )                                                                                                                                                                                   |                       |                                | V    |

| DC Voltage                                                                                                                                                                                                                                     | $V_{INH}$             | -0.3 to V <sub>SUP</sub> + 0.3 |      |

| Transient (Coupled Through 1.0 nF Capacitor, according to ISO7637-2 & ISO7637-3 & "Hardware Requirements for LIN, CAN and Flexray Interfaces in Automotive Applications" specification Rev1.1 / December 2nd, 2009) (See Table 4 and Figure 7) |                       |                                |      |

| - Pulse 1 (test up to the limit for Damage - Class D <sup>(3)</sup> )                                                                                                                                                                          | V <sub>INH(S1)</sub>  | -100                           |      |

| - Pulse 2a (test up to the limit for Damage - Class $D^{(3)}$ )                                                                                                                                                                                | V <sub>INH(S2a)</sub> | +75                            |      |

| - Pulse 3a (test up to the limit for Damage - Class $D^{(3)}$ )                                                                                                                                                                                | V <sub>INH(S3a)</sub> | -150                           |      |

| - Pulse 3b (test up to the limit for Damage - Class D <sup>(3)</sup> )                                                                                                                                                                         | V <sub>INH(S3b)</sub> | +100                           |      |

#### Notes

3. Class D: At least one function of the Transceiver stops working properly during the test and will return into proper operation automatically when the exposure to the disturbance has ended. No physical damage of the IC occurs.

Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                                                                                       | Symbol                         | Value          | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|------|

| ELECTRICAL RATINGS                                                                                                                            |                                |                |      |

| ESD Capability                                                                                                                                |                                |                | V    |

| AECQ100                                                                                                                                       |                                |                |      |

| Human Body Model - JESD22/A114 ( $C_{ZAP}$ = 100 pF, $R_{ZAP}$ = 1500 $\Omega$ )                                                              |                                |                |      |

| LIN1, LIN2 pins versus GND                                                                                                                    | V <sub>ESD1-1</sub>            | ±10.0 k        |      |

| WAKE1, WAKE2 pins versus GND                                                                                                                  | V <sub>ESD1-2</sub>            | ±8.0 k         |      |

| INH1, INH2 pins versus GND                                                                                                                    | V <sub>ESD1-3</sub>            | ±8.0 k         |      |

| All other Pins                                                                                                                                | V <sub>ESD1-4</sub>            | ±4.0 k         |      |

| Charge Device Model - JESD22/C101 (C <sub>ZAP</sub> = 4.0 pF)                                                                                 |                                |                |      |

| Corner pins (Pins 1, 7, 8 and 14)                                                                                                             | V <sub>ESD2-1</sub>            | ±750           |      |

| All other pins (Pins 2-6, 9-13)                                                                                                               | V <sub>ESD2-2</sub>            | ±750           |      |

| Machine Model - JESD22/A115 ( $C_{ZAP}$ = 220 pF, $R_{ZAP}$ = 0 $\Omega$ )                                                                    |                                |                |      |

| All pins                                                                                                                                      | V <sub>ESD3-1</sub>            | ±200           |      |

| According to "Hardware Requirements for LIN, CAN and Flexray Interfaces in Automotive Applications" specification Rev1.1 / December 2nd, 2009 |                                |                |      |

| $(C_{ZAP} = 150 \text{ pF}, R_{ZAP} = 330 \Omega)$                                                                                            |                                |                |      |

| Contact Discharge, Unpowered                                                                                                                  |                                |                |      |

| LIN1, LIN2 pins without capacitor                                                                                                             | V <sub>ESD4-1</sub>            | ±15 k          |      |

| LIN1, LIN2 pins with 220 pF capacitor                                                                                                         | V <sub>ESD4-2</sub>            | ±15 k          |      |

| VSUP (10 μF to ground)                                                                                                                        | V <sub>ESD4-3</sub>            | ±25 k          |      |

| WAKE1, WAKE2 (2*18 k $\Omega$ serial resistor)                                                                                                | V <sub>ESD4-4</sub>            | ±20 k          |      |

| LIN1, LIN2 pins with 220 pF capacitor and indirect ESD coupling (according to ISO10605 - Annex F)                                             | V <sub>ESD4-5</sub>            | ±15 k          |      |

| According to ISO10605 - Rev 2008 test specification                                                                                           |                                |                |      |

| (2.0 k $\Omega$ / 150 pF) - Unpowered - Contact discharge                                                                                     |                                | 105 k          |      |

| LIN1, LIN2 pins without capacitor                                                                                                             | V <sub>ESD5-1</sub>            | ±25 k          |      |

| LIN1, LIN2 pins with 220 pF capacitor                                                                                                         | V <sub>ESD5-2</sub>            | ±25 k          |      |

| VSUP (10 μF to ground)                                                                                                                        | V <sub>ESD5-3</sub>            | ±25 k          |      |

| WAKE1, WAKE2 (2*18 kΩ serial resistor)                                                                                                        | V <sub>ESD5-4</sub>            | ±25 k          |      |

| (2.0 k $\Omega$ / 330 pF) - Powered - Contact discharge                                                                                       | V <sub>ESD6-1</sub>            | ±8 k           |      |

| LIN1, LIN2 pins without capacitor                                                                                                             | VESD6-1<br>V <sub>ESD6-2</sub> | ±8 k           |      |

| LIN1, LIN2 pins with 220 pF capacitor                                                                                                         |                                | ±25 k          |      |

| VSUP (10 μF to ground)                                                                                                                        | V <sub>ESD6-3</sub>            | ±25 k<br>±25 k |      |

| WAKE1, WAKE2 (2*18 kΩ serial resistor)                                                                                                        | V <sub>ESD6-4</sub>            | IZJ N          |      |

#### Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                          | Symbol            | Value                    | Unit |

|------------------------------------------------------------------|-------------------|--------------------------|------|

| Thermal Ratings                                                  |                   |                          |      |

| Operating Temperature Ambient Junction                           | T <sub>A</sub>    | -40 to 125<br>-40 to 150 | °C   |

| Storage Temperature                                              | T <sub>STG</sub>  | -40 to 150               | °C   |

| Thermal Resistance, Junction to Ambient                          | $R_{	heta JA}$    | 150                      | °C/W |

| Peak package reflow temperature during reflow <sup>(4),(5)</sup> | T <sub>PPRT</sub> | Note 5                   | °C   |

| Thermal Shutdown Temperature                                     | T <sub>SHUT</sub> | 150 to 200               | °C   |

| Thermal Shutdown Hysteresis Temperature                          | T <sub>HYST</sub> | 20                       | °C   |

- 4. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 5. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

Table 4. Limits / Maximum test voltage for transient immunity tests

| Test Pulse | V <sub>S</sub> [V] | Pulse repetition<br>frequency [Hz] (1/T <sub>1</sub> ) | Test duration [min] | <b>R</b> <sub>i</sub> [Ω] | Remarks             |

|------------|--------------------|--------------------------------------------------------|---------------------|---------------------------|---------------------|

| 1          | -100               | 2                                                      | 1 for function test | 10                        | t <sub>2</sub> = 0s |

| 2a         | +75                | 2                                                      | 10 for damage test  | 2                         |                     |

| 3a         | -150               | 10                                                     |                     | 50                        |                     |

| 3b         | +100               | 10                                                     |                     | 50                        |                     |

Figure 4. Test Circuit for Transient Test Pulses (V<sub>SUP</sub>)

Figure 5. Test Circuit for Transient Test Pulses (WAKE1,WAKE2)

Figure 6. Test Circuit for Transient Test Pulses (LIN1,LIN2)

Figure 7. Test Circuit for Transient Test Pulses (INH1,INH2)

#### STATIC ELECTRICAL CHARACTERISTICS

**Table 5. Static Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                   | Symbol                                                                                                               | Min         | Тур                         | Max                         | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------|-----------------------------|------|

| VSUP PIN (DEVICE POWER SUPPLY)                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                      |             |                             |                             |      |

| Nominal Operating Voltage                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>SUP</sub>                                                                                                     | 7.0         | 13.5                        | 18.0                        | V    |

| Functional Operating Voltage <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>SUPOP</sub>                                                                                                   | 6.7         | -                           | 27                          | V    |

| Load Dump                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>SUPLD</sub>                                                                                                   | -           | -                           | 40                          | V    |

| Power-On Reset (POR) Threshold  V <sub>SUP</sub> Ramp Down and INH1, INH2 goes High to Low                                                                                                                                                                                                                                                                                                                                                       | V <sub>POR</sub>                                                                                                     | 3.5         | _                           | 5.3                         | V    |

| Power-On Reset (POR) Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>PORHYST</sub>                                                                                                 | -           | 270                         | _                           | mV   |

| V <sub>SUP</sub> Under-voltage Threshold (positive and negative) Transmission disabled and LIN1,LIN2 bus goes in recessive                                                                                                                                                                                                                                                                                                                       | $V_{UVL}, V_{UVH}$                                                                                                   | 5.8         | _                           | 6.7                         | V    |

| V <sub>SUP</sub> Under-voltage Hysteresis (V <sub>UVL</sub> - V <sub>UVH</sub> )                                                                                                                                                                                                                                                                                                                                                                 | V <sub>UVHYST</sub>                                                                                                  | -           | 130                         | _                           | mV   |

| Supply Current LIN1 and LIN2 in Sleep Mode $V_{SUP} \leq 13.5 \text{ V}, \text{ Recessive State} \\ 13.5 \text{ V} < V_{SUP} < 27 \text{ V} \\ V_{SUP} \leq 13.5 \text{ V}, \text{ Shorted to GND}$                                                                                                                                                                                                                                              | <sub>S1</sub><br>  <sub>S2</sub><br>  <sub>S3</sub>                                                                  | 1 1 1       | 12.0<br>-<br>48             | 22<br>36<br>140             | μА   |

| Supply Current LIN1 Normal Mode - LIN2 Sleep Mode (and vice versa)  Bus <sub>1</sub> Recessive, BUS <sub>2</sub> Sleep, Excluding INH1,INH2  OR (Bus <sub>2</sub> Recessive, BUS <sub>1</sub> Sleep, Excluding INH1,INH2)  Bus <sub>1</sub> Dominant, BUS <sub>2</sub> Sleep, Excluding INH1,INH2                                                                                                                                                | I <sub>S_N_REC1,2</sub>                                                                                              | -           | 4.0                         | 5.0                         | mA   |

| OR (Bus <sub>2</sub> Dominant, BUS <sub>1</sub> Sleep, Excluding INH1,INH2)                                                                                                                                                                                                                                                                                                                                                                      | I <sub>S_N_DOM1,2</sub>                                                                                              | _           | 6.0                         | 8.0                         |      |

| Supply Current when LIN1 and LIN2 are in Normal or Slow or Fast Mode  Bus <sub>1</sub> Recessive, Bus <sub>2</sub> Recessive, Excluding INH1,INH2 Output Current  Bus <sub>1</sub> Recessive, Bus <sub>2</sub> Dominant, Excluding INH1,INH2 Output Current  Bus <sub>1</sub> Dominant, Bus <sub>2</sub> Recessive, Excluding INH1,INH2 Output Current  Bus <sub>1</sub> Dominant, Bus <sub>2</sub> Dominant, Excluding INH1,INH2 Output Current | I <sub>S</sub> (REC1,REC2)<br>I <sub>S</sub> (REC1,DOM2)<br>I <sub>S</sub> (DOM1,REC2)<br>I <sub>S</sub> (DOM1,DOM2) | -<br>-<br>- | 8.0<br>12.0<br>12.0<br>12.0 | 9.0<br>13.0<br>13.0<br>16.0 | mA   |

| RXD1, RXD2 OUTPUT PINS (LOGIC)                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                      |             |                             |                             | •    |

| Low Level Output Voltage $I_{IN} \leq 1.5 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>OL</sub>                                                                                                      | 0.0         | _                           | 0.9                         | V    |

| High Level Output Voltage $V_{EN}$ = 5.0 V, $I_{OUT}$ $\leq$ 250 μA $V_{EN}$ = 3.3 V, $I_{OUT}$ $\leq$ 250 μA                                                                                                                                                                                                                                                                                                                                    | V <sub>OH</sub>                                                                                                      | 4.25<br>3.0 | <u>-</u>                    | 5.25<br>3.5                 | V    |

#### Notes

6. Device is functional. All features are operating. Electrical parameters are not guaranteed.

#### **Table 5. Static Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                                                        | Symbol                   | Min  | Тур      | Max | Unit             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|----------|-----|------------------|

| TXD1, TXD2 INPUT PINS (LOGIC)                                                                                                                                                                         |                          |      |          |     |                  |

| Low Level Input Voltage                                                                                                                                                                               | V <sub>IL</sub>          | -    | _        | 0.8 | V                |

| High Level Input Voltage                                                                                                                                                                              | V <sub>IH</sub>          | 2.0  | _        | _   | V                |

| Input Threshold Voltage Hysteresis                                                                                                                                                                    | V <sub>INHYST</sub>      | 100  | 300      | 600 | mV               |

| Pull-up Current Source<br>V <sub>EN</sub> = 5.0 V, 1.0 V < V <sub>TXD</sub> < 3.5 V                                                                                                                   | l <sub>PU</sub>          | -60  | -35      | -20 | μА               |

| EN1, EN2 INPUT PINS (LOGIC)                                                                                                                                                                           |                          |      | <u> </u> | 1   |                  |

| Low Level Input Voltage                                                                                                                                                                               | V <sub>IL</sub>          | _    | _        | 0.8 | V                |

| High Level Input Voltage                                                                                                                                                                              | V <sub>IH</sub>          | 2.0  | _        | _   | V                |

| Input Voltage Threshold Hysteresis                                                                                                                                                                    | V <sub>INHYST</sub>      | 100  | 400      | 600 | mV               |

| Pull-down Resistor                                                                                                                                                                                    | R <sub>PD</sub>          | 100  | 230      | 350 | kohm             |

| LIN PHYSICAL LAYER - TRANSCEIVER LIN (LIN1, LIN2) <sup>(7)</sup>                                                                                                                                      |                          |      |          |     |                  |

| Operating Voltage Range <sup>(8)</sup>                                                                                                                                                                | V <sub>BAT</sub>         | 8.0  | _        | 18  | V                |

| Supply Voltage Range                                                                                                                                                                                  | V <sub>SUP</sub>         | 7.0  | -        | 18  | V                |

| Voltage Range (within which the device is not destroyed)                                                                                                                                              | V <sub>SUP_NON_OP</sub>  | -0.3 | _        | 40  | V                |

| Current Limitation for Driver Dominant State Driver ON, V <sub>BUS</sub> = 18 V                                                                                                                       | I <sub>BUS_LIM</sub>     | 40   | 90       | 200 | mA               |

| Input Leakage Current at the Receiver Driver off; V <sub>BUS</sub> = 0 V; V <sub>BAT</sub> = 12 V                                                                                                     | I <sub>BUS_PAS_DOM</sub> | -1.0 | -        | _   | mA               |

| Leakage Output Current to GND<br>Driver Off; 8.0 V < V <sub>BAT</sub> < 18 V; 8.0 V < V <sub>BUS</sub> < 18 V; V <sub>BUS</sub> $\geq$ V <sub>BAT</sub> ;<br>V <sub>BUS</sub> $\geq$ V <sub>SUP</sub> | lbus_pas_rec             | -    | -        | 20  | μА               |

| Control Unit Disconnected from Ground <sup>(9)</sup> GND <sub>DEVICE</sub> = V <sub>SUP</sub> ; V <sub>BAT</sub> = 12 V; 0 < V <sub>BUS</sub> < 18 V                                                  | I <sub>BUS_NO_GND</sub>  | -1.0 | -        | 1.0 | mA               |

| $V_{BAT}$ Disconnected; $V_{SUP\_DEVICE}$ = GND; 0 V < $V_{BUS}$ < 18 $V^{(10)}$                                                                                                                      | I <sub>BUSNO_BAT</sub>   | -    | _        | 10  | μΑ               |

| Receiver Dominant State <sup>(11)</sup>                                                                                                                                                               | V <sub>BUSDOM</sub>      | -    | -        | 0.4 | V <sub>SUP</sub> |

| Receiver Recessive State <sup>(12)</sup>                                                                                                                                                              | V <sub>BUSREC</sub>      | 0.6  | -        | _   | V <sub>SUP</sub> |

- 7. Parameters guaranteed for 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V.

- 8. Voltage range at the battery level, including the reverse battery diode.

- 9. Loss of local ground must not affect communication in the residual network.

- 10. Node has to sustain the current that can flow under this condition. The bus must remain operational under this condition.

- 11. LIN threshold for a dominant state.

- 12. LIN threshold for a recessive state.

#### **Table 5. Static Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                           | Symbol                    | Min   | Тур | Max   | Unit             |

|------------------------------------------------------------------------------------------|---------------------------|-------|-----|-------|------------------|

| Receiver Threshold Center                                                                | V <sub>BUS_CNT</sub>      |       |     |       | V <sub>SUP</sub> |

| $(V_{TH\_DOM} + V_{TH\_REC})/2$                                                          |                           | 0.475 | 0.5 | 0.525 |                  |

| Receiver Threshold Hysteresis                                                            | V <sub>HYS</sub>          |       |     |       | V <sub>SUP</sub> |

| (V <sub>TH_REC</sub> - V <sub>TH_DOM</sub> )                                             |                           | _     | _   | 0.175 |                  |

| LIN dominant level with 500 $\Omega,$ 680 $\Omega$ and 1.0 $k\Omega$ load on the LIN bus | V <sub>LINDOM_LEVEL</sub> | -     | _   | 0.3   | V <sub>SUP</sub> |

| V <sub>BAT</sub> _SHIFT                                                                  | V <sub>SHIFT_BAT</sub>    | 0.0   | ı   | 11.5% | $V_{BAT}$        |

| GND_SHIFT                                                                                | V <sub>SHIFT_GND</sub>    | 0.0   | ı   | 11.5% | $V_{BAT}$        |

| LIN Wake-up Threshold from Sleep Mode                                                    | V <sub>BUSWU</sub>        | _     | 4.3 | 5.3   | <b>V</b>         |

| LIN Pull-up Resistor to V <sub>SUP</sub>                                                 | R <sub>SLAVE</sub>        | 20    | 30  | 60    | kΩ               |

| LIN internal capacitor <sup>(13)</sup>                                                   | C <sub>LIN</sub>          | _     | _   | 30    | pF               |

| Over-temperature Shutdown <sup>(14)</sup>                                                | T <sub>LINSD</sub>        | 150   | 160 | 200   | °C               |

| Over-temperature Shutdown Hysteresis                                                     | T <sub>LINSD_HYS</sub>    | _     | 20  | _     | °C               |

#### **INH1, INH2 OUTPUT PINS**

| Driver ON Resistance (Normal Mode)        | INH <sub>ON</sub>      |      |     |     | Ω  |

|-------------------------------------------|------------------------|------|-----|-----|----|

| I <sub>INH</sub> = 50 mA                  |                        | _    | _   | 50  |    |

| Current load capability                   | I <sub>INH_load</sub>  |      |     |     | mA |

| From 7.0 V < V <sub>SUP</sub> < 18 V      |                        | _    | -   | 30  |    |

| Leakage Current (Sleep Mode)              | I <sub>LEAK</sub>      |      |     |     | μΑ |

| 0 < V <sub>INH</sub> < V <sub>SUP</sub>   |                        | -5.0 | -   | 5.0 |    |

| Over-temperature Shutdown <sup>(15)</sup> | T <sub>INHSD</sub>     | 150  | 160 | 200 | °C |

| Over-temperature Shutdown Hysteresis      | T <sub>INHSD_HYS</sub> | _    | 20  | -   | °C |

- 13. This parameter is guaranteed by process monitoring but not production tested.

- 14. When an over-temperature shutdown occurs, the LIN transmitter and receiver are in recessive state and INH switched off. This parameter is tested with a test mode on ATE and characterized at laboratory.

- 15. When an over-temperature shutdown occurs, the INH1, INH2 high side are switched off and the LIN transmitter and receiver are in recessive state. This parameter is tested with a test mode on ATE and characterized at laboratory.

#### **Table 5. Static Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                         | Symbol              | Min | Тур | Max | Unit |

|------------------------------------------------------------------------|---------------------|-----|-----|-----|------|

| WAKE1, WAKE2 INPUT PINS                                                | ·                   |     |     |     |      |

| High to Low Detection Threshold (5.5 V < V <sub>SUP</sub> < 7 V)       | V <sub>WUHL1</sub>  | 2.0 | _   | 3.9 | V    |

| Low to High Detection Threshold (5.5 V < V <sub>SUP</sub> < 7 V)       | V <sub>WULH1</sub>  | 2.4 | -   | 4.3 | V    |

| Hysteresis (5.5 V < V <sub>SUP</sub> < 7 V)                            | V <sub>WUHYS1</sub> | 0.2 | -   | 0.8 | V    |

| High to Low Detection Threshold (7 V $\leq$ V <sub>SUP</sub> $<$ 27 V) | V <sub>WUHL2</sub>  | 2.4 | -   | 3.9 | V    |

| Low to High Detection Threshold (7 V $\leq$ V <sub>SUP</sub> $<$ 27 V) | V <sub>WULH2</sub>  | 2.9 | -   | 4.3 | V    |

| Hysteresis (7 V ≤ V <sub>SUP</sub> < 27 V)                             | V <sub>WUHYS2</sub> | 0.2 | -   | 0.8 | V    |

| Wake-up Input Current (V <sub>WAKE</sub> < 27 V)                       | I <sub>WU</sub>     | _   | -   | 5.0 | μΑ   |

#### DYNAMIC ELECTRICAL CHARACTERISTIC

#### **Table 6. Dynamic Electrical Characteristics**

Characteristics noted under conditions  $7.0 \text{ V} < \text{V}_{c}$ < 18 \/ -40 °C < T. < 125 °C GND = 0 \/ unless otherwise noted

| Characteristic                                                                                                                                  | Symbol          | Min        | Тур     | Max   | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|---------|-------|------|

| LIN1, LIN2 PHYSICAL LAYER DRIVERS CHARACTERISTICS FOR NORMAL SLEW RATE - 20.0 KBIT/S SPECIFICATION <sup>(16)(17)</sup> B3663L AND 33663S DEVICE | EC ACCORDING TO | LIN PHYSIC | AL LAYE | २     |      |

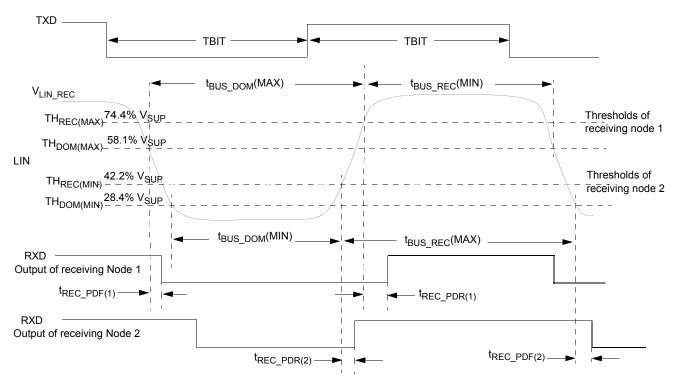

| Duty Cycle 1:                                                                                                                                   | D1              |            |         |       |      |

| $TH_{REC(MAX)} = 0.744 * V_{SUP}; TH_{DOM(MAX)} = 0.581 * V_{SUP}$                                                                              |                 |            |         |       |      |

| D1 = $t_{BUS\_REC(MIN)}/(2 \times t_{BIT})$ , $t_{BIT}$ = 50 $\mu s$ , 7.0 $V \le V_{SUP} \le$ 18 $V$                                           |                 | 0.396      | -       | _     |      |

| Duty Cycle 2:                                                                                                                                   | D2              |            |         |       |      |

| $TH_{REC(MIN)} = 0.422 * V_{SUP}$ ; $TH_{DOM(MIN)} = 0.284 * V_{SUP}$                                                                           |                 |            |         |       |      |

| D2 = $t_{BUS}$ REC(MAX)/(2 x $t_{BIT}$ ), $t_{BIT}$ = 50 $\mu$ s, 7.6 V $\leq$ V <sub>SUP</sub> $\leq$ 18 V                                     |                 | _          | _       | 0.581 |      |

SPECIFICATION<sup>(16)(18)</sup>

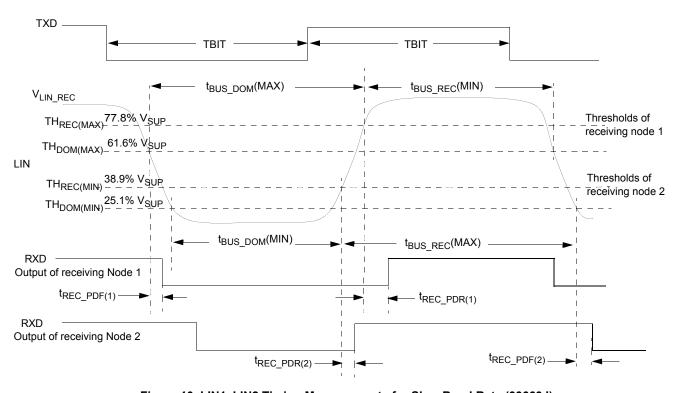

#### **33663J DEVICE**

| Duty Cycle 3:                                                                                       | D3 |       |   |       |  |

|-----------------------------------------------------------------------------------------------------|----|-------|---|-------|--|

| $TH_{REC(MAX)} = 0.778 * V_{SUP}; TH_{DOM(MAX)} = 0.616 * V_{SUP}$                                  |    |       |   |       |  |

| D3 = $t_{BUS\_REC(MIN)}/(2 \times t_{BIT})$ , $t_{BIT}$ = 96 $\mu s$ , 7.0 $V \le V_{SUP} \le 18 V$ |    | 0.417 | - | -     |  |

| Duty Cycle 4:                                                                                       | D4 |       |   |       |  |

| $TH_{REC(MIN)} = 0.389 * V_{SUP}; TH_{DOM(MIN)} = 0.251 * V_{SUP}$                                  |    |       |   |       |  |

| D4 = $t_{BUS\_REC(MAX)}/(2 \times t_{BIT})$ , $t_{BIT}$ = 96 $\mu$ s, 7.6 $V \le V_{SUP} \le 18 V$  |    | _     | - | 0.590 |  |

#### LIN1, LIN2 PHYSICAL LAYER - DRIVERS CHARACTERISTICS FOR FAST SLEW RATE

| The second of th | Fast Bit Rate (Programming Mode) | BR <sub>FAST</sub> | _ | _ | 100 | kBit/s |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------|---|---|-----|--------|

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------|---|---|-----|--------|

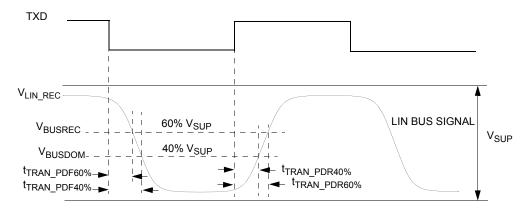

#### LIN1, LIN2 PHYSICAL LAYER - TRANSMITTER CHARACTERISTICS FOR NORMAL SLEW RATE - 20.0 KBIT/SEC(19) **33663S DEVICE**

| Symmetry of Transmitter delay <sup>(20)</sup> $t_{TRAN\_SYM} = MAX (t_{TRAN\_SYM60\%}, t_{TRAN\_SYM40\%})$ | t <sub>TRAN_SYM</sub> | -7.25 | - | 7.25 | μS |

|------------------------------------------------------------------------------------------------------------|-----------------------|-------|---|------|----|

| ttran_sym60% =   ttran_pdf60% - ttran_pdr60%  <br>ttran_sym40% =   ttran_pdf40% - ttran_pdr40%             |                       |       |   |      |    |

| 1RAN_31W40% 1 1RAN_FDF40% - 1RAN_FDR40% 1                                                                  |                       |       |   |      |    |

- 16. Bus load R\_{BUS} and C\_{BUS} 1.0 nF / 1.0 k $\Omega$ , 6.8 nF / 660  $\Omega$ , 10 nF / 500  $\Omega$ . Measurement thresholds: 50% of TXD signal to LIN signal threshold defined at each parameter. See Figure 8.

- 17. See Figure 9

- 18. See <u>Figure 10</u>

- 19.  $V_{SUP}$  from 7.0 to 18 V, bus load  $R_{BUS}$  and  $C_{BUS}$  1.0 nF / 1.0 k $\Omega$ , 6.8 nF / 660  $\Omega$ , 10 nF / 500  $\Omega$ . Measurement thresholds: 50% of TXD signal to LIN signal threshold defined at each parameter. See Figure 8.

- 20. See Figure 11

#### **Table 6. Dynamic Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                         | Symbol                      | Min  | Тур | Max | Unit |  |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|-----|-----|------|--|

| IN1, LIN2 PHYSICAL LAYER - RECEIVERS CHARACTERISTICS ACCORDING LIN2.1 <sup>(21)</sup><br>3663L AND 33663J AND 33663S   |                             |      |     |     |      |  |

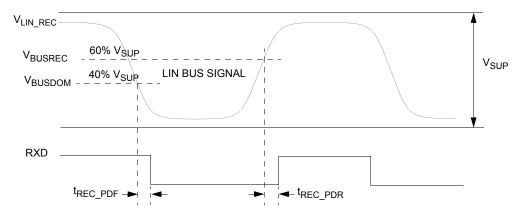

| Propagation Delay and Symmetry <sup>(22)</sup>                                                                         |                             |      |     |     | μS   |  |

| Propagation Delay of Receiver, t <sub>REC_PD</sub> = MAX (t <sub>REC_PDR</sub> , t <sub>REC_PDF</sub> )                | t <sub>REC_PD</sub>         | _    | _   | 6.0 |      |  |

| Symmetry of Receiver Propagation Delay, t <sub>REC_PDF</sub> - t <sub>REC_PDR</sub>                                    | t <sub>REC_SYM</sub>        | -2.0 | _   | 2.0 |      |  |

| LIN1, LIN2 PHYSICAL LAYER: RECEIVER CHARACTERISTICS WITH TIGH<br>33663S DEVICE                                         | ITEN LIMITS <sup>(21)</sup> |      |     |     |      |  |

| Propagation Delay and Symmetry <sup>(22)</sup>                                                                         |                             |      |     |     | μS   |  |

| Propagation Delay of Receiver, t <sub>REC_PD</sub> = MAX (t <sub>REC_PDR</sub> , t <sub>REC_PDF</sub> )                | t <sub>REC_PD_S</sub>       | _    | _   | 5.0 |      |  |

| Symmetry of Receiver Propagation Delay, t <sub>REC_PDF</sub> - t <sub>REC_PDR</sub>                                    | t <sub>REC_SYM_</sub> s     | -1.3 | _   | 1.3 |      |  |

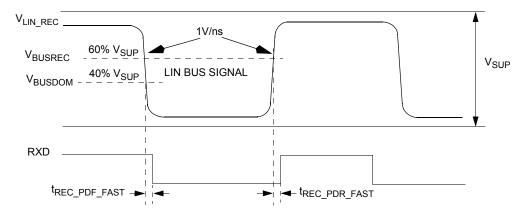

| LIN1, LIN2 PHYSICAL LAYER: RECEIVER CHARACTERISTICS - LIN SLOP<br>33663S DEVICE                                        | PE 1V/ns <sup>(21)</sup>    |      |     |     |      |  |

| Propagation Delay and Symmetry <sup>(23)</sup>                                                                         |                             |      |     |     | μS   |  |

| Propagation Delay of Receiver, t <sub>REC_PD_FAST</sub> = MAX (t <sub>REC_PDR_FAST</sub> , t <sub>REC_PDF_FAST</sub> ) | tREC_PD_FAST                | _    | _   | 6.0 |      |  |

| Symmetry of Receiver Propagation Delay, t <sub>REC_PDF_FAST</sub> - t <sub>REC_PDR_FAST</sub>                          | t <sub>REC_SYM_FAST</sub>   | -1.3 | _   | 1.3 |      |  |

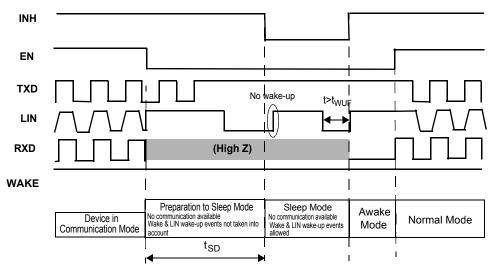

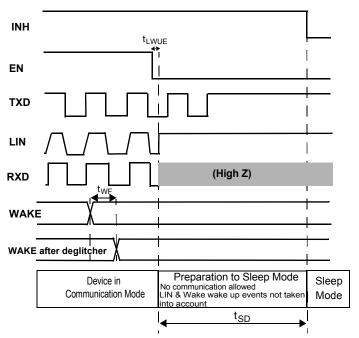

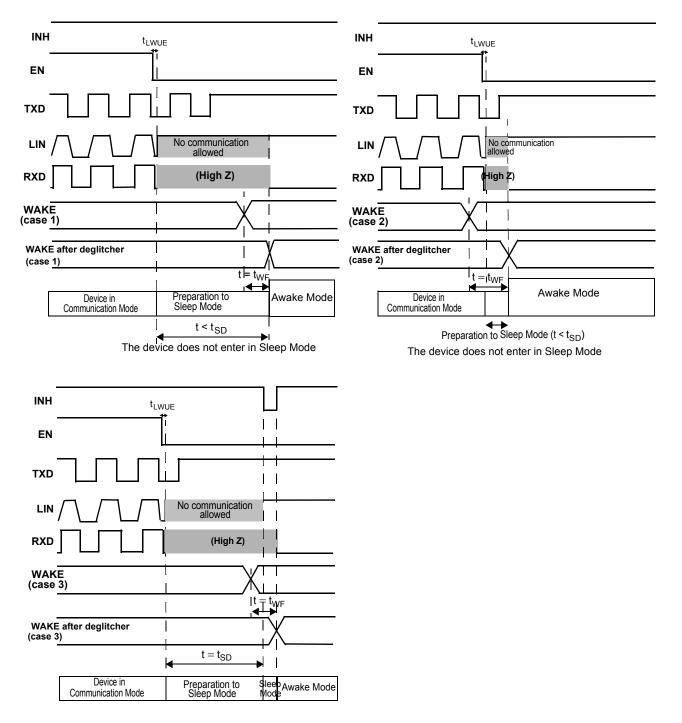

| SLEEP MODE AND WAKE-UP TIMINGS                                                                                         | I                           | I.   | l   | I.  |      |  |

| Sleep Mode Delay Time <sup>(24)</sup>                                                                                  | t <sub>SD</sub>             |      |     |     | μs   |  |

| after EN High to Low to INH High to Low with 100μA load on INH                                                         |                             | 50   | _   | 91  |      |  |

| WAKE-UP TIMINGS                                                                                                        |                             |      |     |     |      |  |

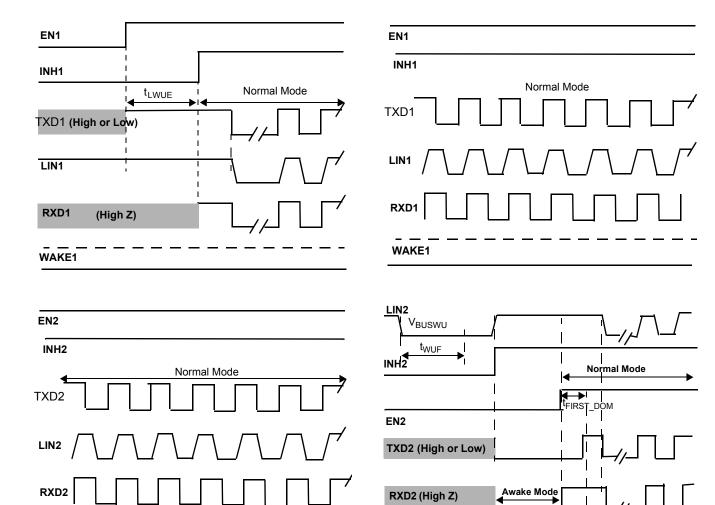

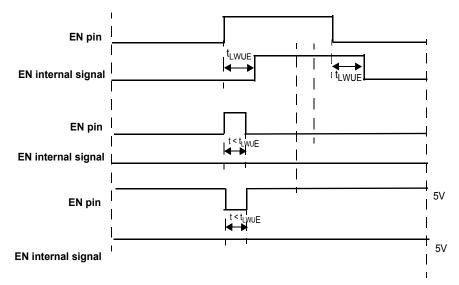

| Bus Wake-up Deglitcher (Sleep Mode) (25)                                                                               | t <sub>WUF</sub>            | 40   | 70  | 100 | μS   |  |

| EN Wake-up Deglitcher (26)                                                                                             | t <sub>LWUE</sub>           |      |     |     | μS   |  |

| EN High to INH Low to High                                                                                             | _                           | _    | _   | 15  |      |  |

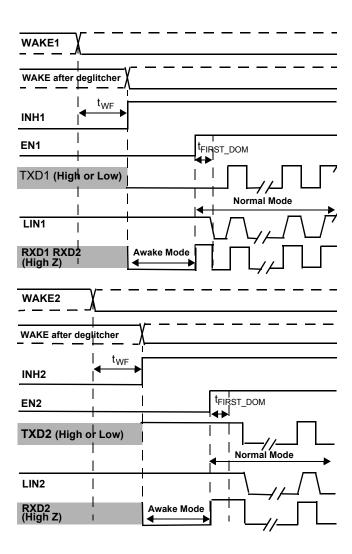

| Wake-up Deglitcher (27)                                                                                                | t <sub>WF</sub>             |      |     |     | μS   |  |

| Wake state change to INH Low to High                                                                                   |                             | 10   | 48  | 70  |      |  |

- 21.  $V_{SUP}$  from 7.0 to 18 V, bus load  $R_{BUS}$  and  $C_{BUS}$  1.0 nF / 1.0 k $\Omega$ , 6.8 nF / 660  $\Omega$ , 10 nF / 500  $\Omega$ . Measurement thresholds: 50% of TXD signal to LIN signal threshold defined at each parameter. See Figure 8.

- 22. See Figure 12

- 23. See <u>Figure 13</u>

- 24. See <u>Figures 22</u> and <u>23</u>

- 25. See Figures 15 and  $\underline{17}$

- 26. See Figures 14, 18, 22, and 23

- 27. See Figures 16, 22, and 23

#### **Table 6. Dynamic Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                      | Symbol                 | Min   | Тур | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------|------------------------|-------|-----|------|------|

| TXD TIMING                                                                                                          |                        |       |     |      |      |

| TXD Permanent Dominant State Delay <sup>(28)</sup>                                                                  | t <sub>TXDDOM</sub>    | 3.75  | 5.0 | 6.25 | ms   |

| FIRST DOMINANT BIT VALIDATION                                                                                       |                        |       |     |      |      |

| First dominant bit validation delay when device in Normal Mode <sup>(29)</sup>                                      | t <sub>FIRST_DOM</sub> | _     | 50  | 80   | ms   |

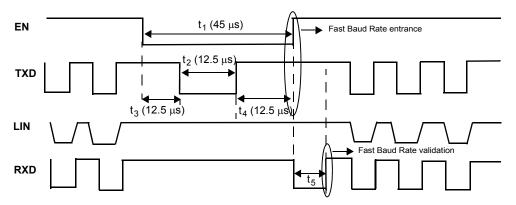

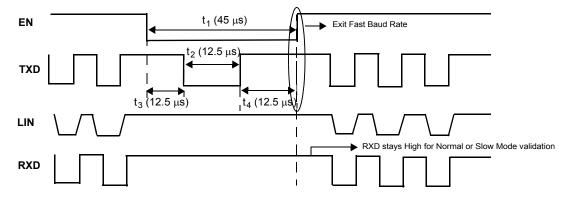

| FAST BAUD RATE TIMING                                                                                               |                        |       |     |      |      |

| EN Low Pulse Duration to Enter in Fast Baud Rate Using Toggle Function (30) EN High to Low and Low to High          | t <sub>1</sub>         | _     | _   | 45   | μS   |

| TXD Low Pulse Duration to Enter in Fast Baud Rate Using Toggle Function (30)                                        | t <sub>2</sub>         | 12.5  | _   | _    | μs   |

| Delay Between EN Falling Edge and TXD Falling Edge to Enter in Fast Baud Rate Using Toggle Function <sup>(30)</sup> | t <sub>3</sub>         | 12.5  | _   | _    | μs   |

| Delay Between TXD Rising Edge and EN Rising Edge to Enter in Fast Baud Rate Using Toggle Function <sup>(30)</sup>   | t <sub>4</sub>         | 12.5  | _   | _    | μs   |

| RXD Low Level duration after EN rising edge to validate the Fast Baud Rate entrance <sup>(30)</sup>                 | t <sub>5</sub>         | 1.875 |     | 6.25 | μs   |

#### Notes

- 28. The LIN is in recessive state and the receiver is still active

- 29. See Figures 14, 15, 16, and 21

- 30. See Figures 19 and 20

#### **TIMING DIAGRAMS**

Note R<sub>0</sub> and C<sub>0</sub>: 1.0 k $\Omega$ /1.0 nF, 660  $\Omega$ /6.8 nF, and 500  $\Omega$ /10 nF.

**Figure 8. Test Circuit for Timing Measurements**

Figure 9. LIN1, LIN2 Timing Measurements for Normal Baud Rate (33663L, 33663S)

Figure 10. LIN1, LIN2 Timing Measurements for Slow Baud Rate (33663J)

Figure 11. LIN1, LIN2 Transmitter Timing for 33663S

Figure 12. LIN1, LIN2 Receiver Timing

Figure 13. LIN1, LIN2 Receiver Timing LIN Slope 1.0 V/ns

#### **FUNCTIONAL DIAGRAMS**

WAKE2

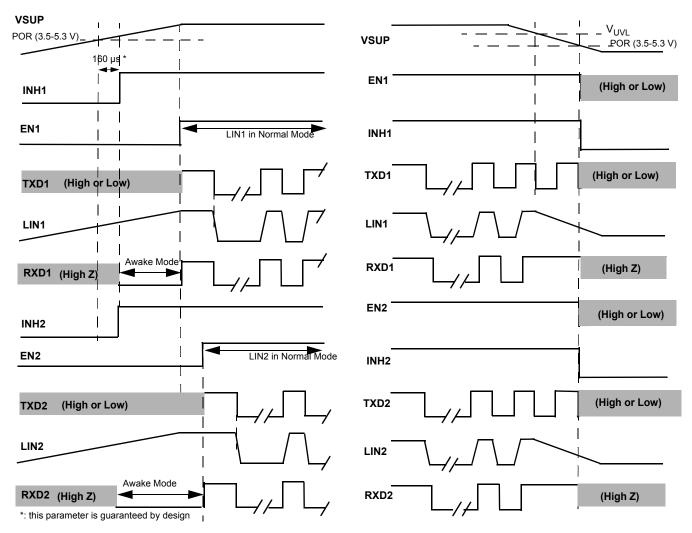

Figure 14. LIN Module 1 EN1 Pin Wake-up with TXD1 High & LIN Module 2 in Normal Mode

WAKE2

Figure 15. LIN Module 1 in Normal Mode & LIN Module 2 LIN2 Wake-up with TXD2 LOW

Figure 16. LIN Module 1 Wake1 Pin Wake-up with TXD1 Low & LIN Module 2 Wake2 Pin Wake-up with TXD2 High

Figure 17. Bus Wake-up with LIN bus in Dominant During the Preparation to Sleep Mode (same sequence for LIN1 & LIN2)

Figure 18. EN1, EN2 Pin Deglitcher

Figure 19. Fast Baud Rate Selection (Toggle Function) for LIN1 or LIN2

Figure 20. Fast Baud Rate Mode Exit (Back to Normal or Slow Slew Rate) for LIN1 or LIN2

Figure 21. Power Up and Down Sequences

Figure 22. Sleep Mode Sequence for LIN1 or LIN2

Figure 23. Examples of Sleep Mode Sequences for LIN1 or LIN2

#### **FUNCTIONAL DESCRIPTION**

#### INTRODUCTION

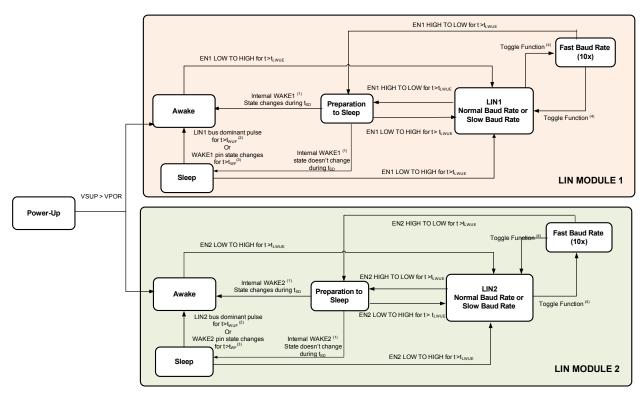

The 33663L and 33663J are both a Physical Layer component dedicated to automotive LIN sub-bus applications.

The 33663L features include a 20 kbps baud rate and the 33663J a 10 kbps baud rate. Both integrate fast baud rate for test and programming modes, excellent ESD robustness, immunity against disturbance, and radiated emission performance. They have safe behavior, in case of a LIN bus short-to-ground, or a LIN bus leakage during low power mode.

Digital inputs are 5.0 and 3.3 V compatible without any external required components.

The INH1 and INH2 outputs may be used to control an external voltage regulator, or to drive a LIN bus pull-up resistor.

#### **FUNCTIONAL PIN DESCRIPTION**

#### **POWER SUPPLY PIN (VSUP)**

The VSUP supply pin is the power supply pin for the 33663L or 33663J. In an application, the pin is connected to a battery through a serial diode, for reverse battery protection. The DC operating voltage is from 7.0 to 18 V. This pin sustains standard automotive condition, such as 40 V during load dump. To avoid a false bus message, an under-voltage on VSUP disables the transmission path (from TXD to LIN) when  $V_{SUP}$  falls below 6.7 V. Supply current in the Sleep mode is typically 6.0  $\mu$ A for one LIN Module.

#### **GROUND PIN (GND)**

In case of a ground disconnection at the module level, the 33663L and 33663J do not have significant current consumption on the LIN bus pin when in the recessive state.

#### LIN BUS PIN (LIN1, LIN2)

The LIN1 and LIN2 pins represent the single-wire bus transmitter and receiver. It is suited for automotive bus systems, and is compliant to the LIN bus specification 1.3, 2.0, 2.1, and SAEJ2602-2.

The LIN interface is only active during Normal mode.

#### **Transmitter Characteristics**

The LIN driver is a low side MOSFET with internal over-current thermal shutdown. An internal pull-up resistor with a serial diode structure is integrated, so no external pull-up components are required for the application in a slave node. An additional pull-up resistor of 1.0 k $\Omega$  must be added when the interface is used in the master node.

The LIN pin exhibits no reverse current from the LIN bus line to  $V_{SUP}$ , even in the event of a GND shift or  $V_{SUP}$  disconnection. The 33663 is tested according to the application conditions (i.e. in normal mode and recessive state during communication).

The transmitter has a 20 kbps baud rate (Normal baud rate) for the 33663L and 33663S devices, or 10 kbps baud rate (Slow baud rate) for the 33663J device.

33663

As soon as the device enters Normal mode, the LIN transmitter will be able to send the first dominant bit only after the  $t_{\text{FIRST\_DOM}}$  delay.  $t_{\text{FIRST\_DOM}}$  delay has no impact on the receiver. The receiver will be enabled as soon as the device enters Normal mode.

#### **Receiver Characteristics**

The receiver thresholds are ratiometric with the device supply pin.

If the  $V_{SUP}$  voltage goes below the  $V_{SUP}$  under-voltage threshold ( $V_{UVL}$ ,  $V_{UVH}$ ), the bus LIN1 and bus LIN2 enter into a recessive state even if communication is sent to TXD1 or TXD2.

For the LIN Module 1, in case of LIN1 Thermal Shutdown, the transceiver and receiver are in recessive and INH1 turned off. When the temperature is below the T<sub>LINSD</sub>, INH1 and LIN1 will be automatically enabled. The same behavior is valid for LIN Module 2.

For each LIN Module, the Fast Baud Rate selection is reported by the RXD pin. Fast Baud Rate is activated by the toggle function (See Figure 19). At the end of the toggle function, just after EN rising edge, RXD pin is kept low for  $t_5$  to flag the Fast Baud Rate entry (See Figure 19).

To exit the Fast Baud Rate and return in Normal or Slow baud rate, a toggle function is needed. At the end the toggle function, RXD pin stays high to signal Fast Baud Rate exit (See <u>Figure 20</u>). The device enters into Fast Baud Rate at room and hot temperature.

#### **DATA INPUT PINS (TXD1, TXD2)**

The TXD1 and TXD2 inputs pins are the MCU interface to control the state of the LIN1 and LIN2 outputs. When TXD1 (TXD2) is LOW (dominant), LIN1 (LIN2) output is LOW; when TXD1 (TXD2) is HIGH (recessive), the LIN1 (LIN2) output transistor is turned OFF. TXD1/TXD2 pins thresholds are 3.3 V and 5.0 V compatible.

These pins have an internal pull-up current source to force the recessive state if the input pins are left floating.

If TXD1 (TXD2) stays low (dominant sate) more than 5.0 ms (typical value), the LIN1 (LIN2) transmitter of LIN Module goes automatically into recessive state.

#### **DATA OUTPUT PINS (RXD1, RXD2)**

Each LIN Modules integrate the same RXD output structure and functionality. Both pins are independent. The following description is the same for both.

RXD output pin is the MCU interface, which reports the state of the LIN bus voltage.

In Normal or Slow baud rate, LIN HIGH (recessive) is reported by a high voltage on RXD; LIN LOW (dominant) is reported by a low voltage on RXD. The RXD output structure is a tristate output buffer.

Figure 24. RXD interface

The RXD output pins are the receiver output of the LIN interface. The low level is fixed. The high level is dependent on EN voltage. If EN is set at 3.3 V, RXD  $V_{OH}$  is 3.3 V. If EN is set at 5.0 V, RXD  $V_{OH}$  is 5.0 V. The RXD1 and RXD2  $V_{OH}$  level can be defined independently.

In sleep mode, RXD are high-impedance. When a wake-up event is recognized from the WAKE pin or from the LIN bus pin, RXD is pulled LOW to report the wake-up event. An external pull-up resistor may be needed.

#### **ENABLE INPUT PINS (EN1, EN2)**

EN1 (EN2) input pin controls the operation mode of the interface. If EN1 (EN2) = 1, the interface is in Normal mode, TXD1 (TXD2) to LIN1 (LIN2) after  $t_{\text{FIRS\_DOM}}$  delay and LIN1 (LIN2) to RXD1 (RXD2) paths are both active. EN1 (EN2) pin thresholds are 3.3 V and 5.0 V compatible. RXD1 (RXD2)  $V_{\text{OH}}$  level follows EN1 (EN2) pin high level. One LIN Module enters the Sleep Mode by setting EN1 (EN2) LOW for a delay higher than  $t_{\text{SD}}$  (70  $\mu$ s typ. value) and if the WAKE1 (WAKE2) pin state doesn't change during this delay. (see Figure 22). Both LIN Modules enter Sleep Mode if EN1 & EN2 LOW.

A combination of the logic levels on EN1 (EN2) and TXD1 (TXD2) pins allows the device to enter in Fast Baud Rate mode of operation (see Figure 19).

#### **INHIBIT OUTPUT PINS (INH1, INH2)**

The INH1 (INH2) output pin is connected to an internal high side power MOSFET. The pin has two possible main functions. It can be used to control an external switchable voltage regulator having an inhibit input. It can also be used to drive the LIN bus external resistor in the master node application, thanks to its high drive capability. This is illustrated in <a href="Figure 26">Figure 26</a>.

In Sleep mode, INH1 (INH2) is turned OFF. If a voltage regulator inhibit input is connected to INH1 (INH2), the regulator will be disabled. If the master node pull-up resistor is connected to INH1 (INH2), the pull-up resistor will be unpowered and left floating.

In case of a INH1 (INH2) thermal shutdown, the high side is turned off and the LIN1 (LIN2) transmitter and receiver are in recessive state. An external 10 to 100 pF capacitor on INH1 (INH2) pin is advised in order to improve EMC performances.

#### WAKE INPUT PINS (WAKE1, WAKE2)

The WAKE1 (WAKE2) pin is a high-voltage input used to wake-up the device from the Sleep mode. WAKE1 (WAKE2) is usually connected to an external switch in the application.

The WAKE1 (WAKE2) pin has a special design structure and allows wake-up from both HIGH to LOW or LOW to HIGH transitions. When entering into Sleep mode, the corresponded LIN Module monitors the state of its WAKE pin and stores it as a reference state. The opposite state of this reference state will be the wake-up event used by the LIN Module to enter again into Normal mode.

If the WAKE1 (WAKE2) pin state changes during the Sleep mode Delay Time ( $t_{SD}$ ) or before EN1 (EN2) goes low with a deglitcher lower than  $t_{WF}$ , the LIN Module will not enter in Sleep mode, but will go into Awake mode (See <u>Figure 23</u>).

An internal filter is implemented to avoid false wake-up event due to parasitic pulses (See Figure 16). WAKE1 (WAKE2) pin input structure exhibits a high-impedance, with extremely low input current when voltage at this pin is below 27 V. Two serial resistors should be inserted in order to limit the input current mainly during transient pulses and ESD. The total recommended resistor value is 33 k $\Omega$ . An external 10 to 100 nF capacitor is advised for better EMC and ESD performances.

**Important** The WAKE1 (WAKE2) pin should not be left open. If the wake-up function is not used, WAKE1 (WAKE2) should be connected to ground to avoid a false wake-up.

#### **FUNCTIONAL DEVICE OPERATION**

#### **OPERATIONAL MODES**